# Pletronics, Inc.

19013 36<sup>th</sup> Ave. West PO Box 2607 Lynnwood, Washington 98036 U.S.A. T: 1-425-776-1880 F: 1-425-776-2760 E: ple-sales@pletronics.com www.pletronics.com

Effective January 1, 2008

PE11xxBY

PE33xxBY

PE37xxBY

Devices are OBSOLETE

This has been discontinued because:

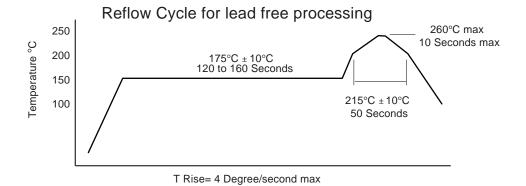

- the difficulty of the older design to assemble well in the newer RoHS compliant high temperature reflow processes.

- the cover assembly was not meeting some of the cleaning and assembly needs of the newer processes.

- the components needed to make these parts are no longer available.

This requirement is best met by using a PE99xxDV oscillator and a -3.3V regulator and operating the device from the 5.0V supply.

# **Differential PECL Series**

- Differential PECL Output, Some with Enable/ Disable Function

- Available in 9 Different Package/Configurations, See Next Pages

#### Standard Specifications

Overall Frequency Stability ± 50 PPM, ± 25 PPM, ± 20 PPM over Operating Temperature Range Operating Temperature Range 0 to +80°C is standard, but can be extended to - 40 to +85°C

Storage Temperature Range - 55 to +125°C

Supply Voltage (Vcc) 3.3 volts  $\pm$  5% standard, but 5.0 volts or 2.5 volts also available. See Test Cirucit 5.

Supply Current (Icc) < 250 MHz = 90 mA maximum, 250 MHz and above = 100 mA maximum

Output High Level 2.275 V minimum referenced to Ground, Vcc = 3.300V,

0.975 V minimum referenced to termination voltage, - 1.025 V minimum referenced to Vcc

Output Low Level 1.680 V maximum referenced to Ground, Vcc = 3.300V,

0.380 V maximum referenced to termination voltage,

- 1.620 V maximum referenced to Vcc

Output Symmetry 45/55% referenced to 50% of amplitude

Output Rise & Fall (Tr & Tf) 1.0 nS maximum when Vth is 10% and 90% of waveform

Jitter 1 pS RMS maximum measured from 12 kHz to 20 MHz from Fnominal

E/D Internal Pullup 50 kohm minimum to Vcc

V disable 0.3 Vcc maximum referenced to Ground V enable 0.7 Vcc minumum referenced to Ground

#### PE7745D only Output Enable / Disable

High Level Input Current

-20 uA maximum at Enable / Disable Pin = 0.7 Vcc

Low Level Input Current

-20 uA maximum at Enable / Disable Pin = 0.7 Vcc

Output Enable Time 200 nS maximum at output enable or 1 mS maximum at output enabled and stable

Output Disable Time 200 nS maximum at output disable

Vcc Supply Current disabled < 1 mA. Both outputs are high impedance when disabled.

#### All other models Output Enable/Disable (E/D)

Output Enable Time 100 nS maximum

Output Disable Time 100 nS maximum

When Disabled Q Output = Logic Low, QN Output = Logic High. Both Outputs are active

Note 1: PECL and ECL are identical circuits.

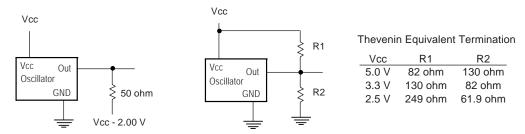

ECL has the most positive pin as ground and is ideally terminated by 50 ohms to  $\,$  - 2.00 V

PECL has the most negative pin as ground and is ideally terminated by 50 ohms to the most (positive voltage less 2.00 V)

#### Mechanical: See Next Pages

# B Package PECL Series PE1145T, PE1145B, PE3345B, PE3745B

- Differential PECL Output with Enable/ Disable Function, 5.0 Vcc or 3.3 Vcc

- 6 Pad 14x10x3mm Leadless Surface Mount Clock Oscillator

1.50 MHz - 650.00 MHz

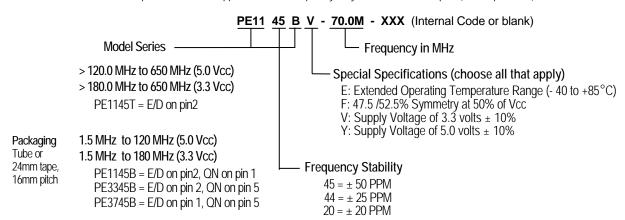

#### **Part Numbering Guide**

Portions of the part number that appear after the frequency may not be marked on part (C of C provided)

Consult factory for available frequencies and specs. Not all options available for all frequencies. A special part number may be assigned. Frequency Stability is inclusive of frequency shifts due to calibration, temperature, supply voltage, shock, vibration and load

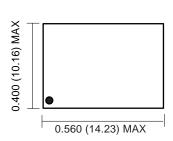

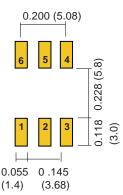

#### Mechanical: inches (mm)

#### not to scale

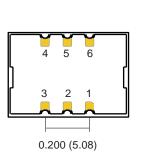

#### Solder Pads

Due to part size and factory abilities, part marking may vary from lot to lot and may contain our part number or an internal code.

#### PE1145T

| PIN | SIGNAL |

|-----|--------|

| 1   | N.C.   |

| 2   | E/D    |

| 3   | GND    |

| 4   | Q OUT  |

| 5   | QN OUT |

| 6   | Vcc    |

> 180.0 MHz to 650.0 MHz (3.3 Vcc)

> 120.0 MHz to 650.0 MHz (5.0 Vcc)

Jun 2004

PE1145B PE3345B PE3745B

| PIN | SIGNAL |   | PIN | SIGNAL |   | PIN | SIGNAL |

|-----|--------|---|-----|--------|---|-----|--------|

| 1   | QN OUT |   | 1   | N.C.   |   | 1   | E/D    |

| 2   | E/D    |   | 2   | E/D    |   | 2   | N.C.   |

| 3   | GND    |   | 3   | GND    |   | 3   | GND    |

| 4   | Q OUT  |   | 4   | Q OUT  |   | 4   | Q OUT  |

| 5   | N.C.   |   | 5   | QN OUT |   | 5   | QN OUT |

| 6   | Vcc    |   | 6   | Vcc    |   | 6   | Vcc    |

|     |        | L |     |        | ı |     |        |

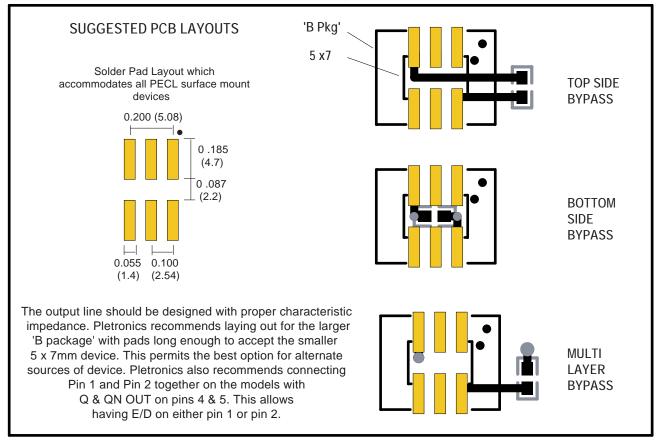

1.5 MHz to 180.0 MHz (3.3 Vcc) 1.5 MHz to 120.0 MHz (5.0 Vcc) See page 6 for Layout Guidelines

# **PECL and LVDS Layout Guidelines**

For Optimum Jitter Performance, Pletronics recommends:

- A ground plane under the device with any other signals below the ground plane

- · Minimize other RF signals near device

- No large transient signals (both current and voltage) should be routed under the device

- Do not layout near a large magnetic field such as a high frequency switching power supply

- Do not place near piezoelectric buzzers or mechancial fans

Mar 2004

# **PECL and LVDS Layout Guidelines Continued**

#### **PECL Terminations:**

Suggested Terminations for 50 ohm impedance matched termination

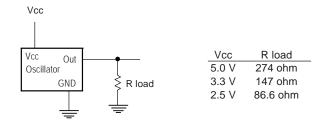

Simple termination for NON impedance matched termination

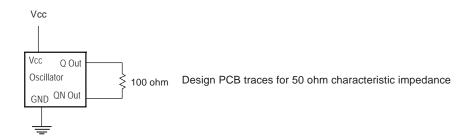

#### **LVDS Terminations:**

### **Mixed System Power Supply:**

**PECL** To use multiple supply voltages requires level translation. Direct circuit connection is not valid.

Mixed supply voltages are allowed. No translation is necessary. (ECL is returned to the most positive supply and this is common to all circuits)

LVDS Mixed supply voltages are allowed. LVDS signal levels are power supply independent. 3.3 V LVDS oscillators properly interface 2.5 V Logic Arrays for example.

Mar 2004